定义

SPI是串行外设接口(Serial Peripheral Interface)的缩写,是一种高速的,全双工,同步的通信总线

- 并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为

PCB的布局上节省空间,提供方便 - 主要应用在

FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

缺点

- 抗干扰能力比 RS422/485 要差,不适合远距离传输。

- 没有与 IIC 协议类似的应答机制。

- 最慢的设备决定了传输的速度。

- 没有官方标准,因此经常用于特定于应用程序的实现。

- 没有流量控制。

SPI信号线

SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)

- MISO: 主设备输入/从设备输出引脚。该引脚在从模式下发送数据,在主模式下接收数据。

- MOSI: 主设备输出/从设备输入引脚。该引脚在主模式下发送数据,在从模式下接收数据。

- SCLK:时钟信号必须由主设备提供给从设备(或在多个从设备设置的情况下提供给所有从设备)。

- CS/SS:从设备片选信号,由主设备控制。它的功能是用来作为“片选引脚”,也就是选择指定的从设备,让主设备可以单独地与特定从设备通讯,避免数据线上的冲突。

SCLK时钟信号触发机制

- 边沿触发和电平触发。

- 最常用的触发是边沿触发,有两种类型:上升沿(时钟从低到高的转换)和下降沿(从高到低的转换)

- 根据接收器的配置方式,在检测到边沿时,接收器将从下一位开始在数据总线上查找数据。

- 以相对较低的成本提供了高速安全数据传输和相当简单的硬件(如移位寄存器)。

SPI设备选择

SPI是单主设备( single-master )通信协议,这意味着总线中的只有主设备能发起通信。

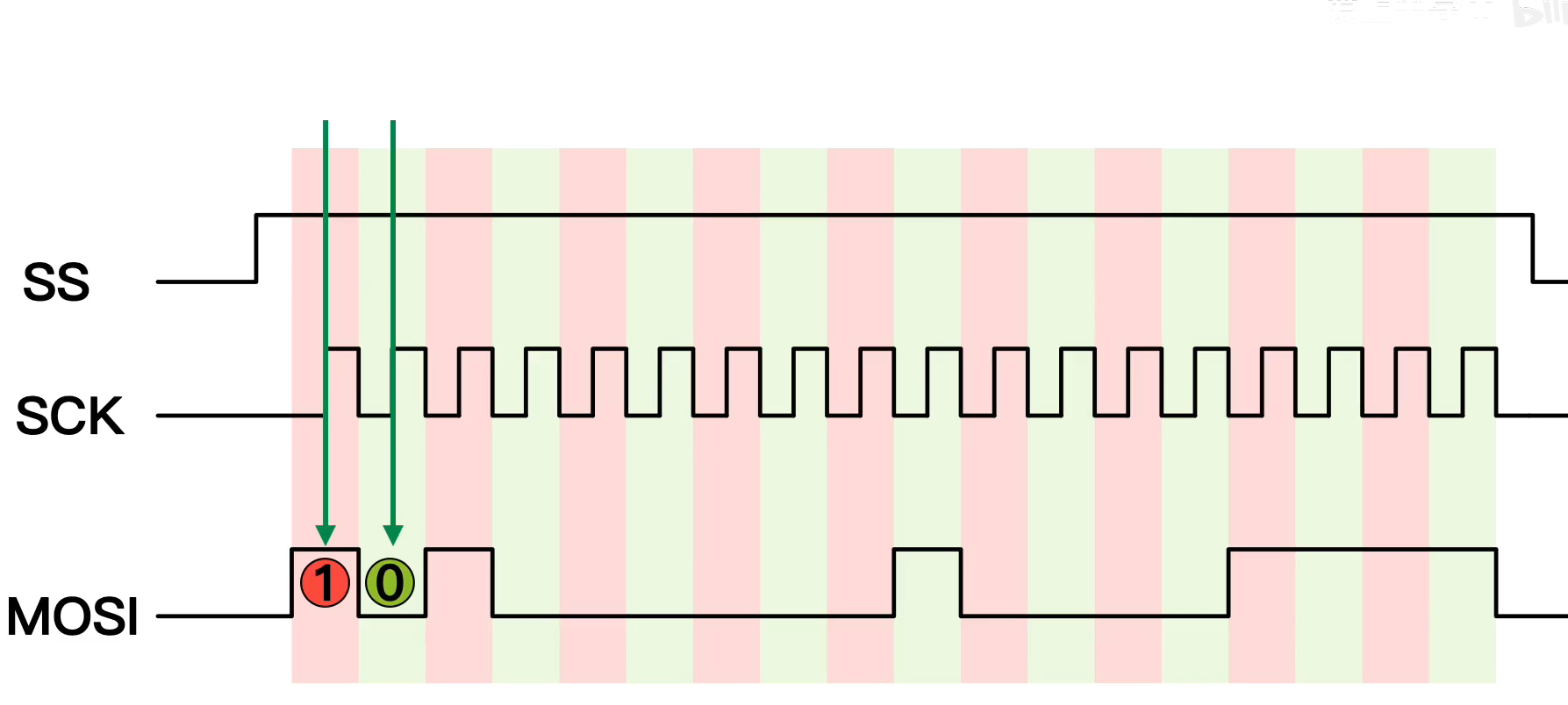

数据交换

数据通常先从最高有效位(MSB)移出。在时钟边沿,主器件和子器件都会向其对应方移出一位。在下一个时钟边沿,每个接收器都会对传输的位进行采样并将其作为新的最低有效位存储在移位寄存器中。在所有的位都被移出和移入之后,主器件和子器件就交换了寄存器值。如果需要交换更多数据,则重新加载移位寄存器并重复该过程。传输可以持续任意数量的时钟周期。完成后,主器件停止切换时钟信号,并且通常会取消选择子器件。

- 每次SPI是主从设备在交换数据。因为 SPI 协议规定一个 SPI 设备不能在数据通信过程中仅仅只充当一个 发送者(Transmitter) 或者 接收者(Receiver)。

- 主设备它首先拉低[从设备]对应的SS线(SS是低电平有效)

- 接着开始发送工作脉冲到时钟线上,在相应的脉冲时间上,[主设备]把信号发到MOSI实现“写”,同时可对MISO采样而实现“读”。

SPI四种模式

时钟信号通过时钟极性 (

CPOL) 和 时钟相位 (CPHA) 控制着两个SPI设备间何时数据交换以及何时对接收到的数据进行采样,来保证数据在两个设备之间是同步传输的。

- 设备的模式不可改变

- 主从设备模式须保持一致

- 时钟极性决定时钟的状态。极性,会直接影响

SPI总线空闲时的时钟信号是高电平还是低电平。 - 一个时钟周期会有

2个跳变沿。而相位,直接决定SPI总线从跳变沿开始采样数据,为0表示从第一个跳变沿采样~

| 模式 | CPOL | SCLK 空闲状态 | CPHA | 数据采样时间 | 数据发送时间 |

|---|---|---|---|---|---|

| Mode0 | 0 | 低电平 | 0 | 上升沿 | 下降沿 |

| Mode1 | 0 | 低电平 | 1 | 下降沿 | 上升沿 |

| Mode2 | 1 | 高电平 | 0 | 下降沿 | 上升沿 |

| Mode3 | 1 | 高电平 | 1 | 上升沿 | 下降沿 |

| 数据采样=准备数据 |

CPOL: 时钟极性,定义了时钟信号的空闲状态。

- 当CPOL=0 时,时钟空闲状态为低电平。

- 当CPOL=1 时,时钟空闲状态为高电平。

CPHA: 时钟相位,定义了数据的采样时间。

- 当CPHA=0时,在时钟的第一个跳变沿(上升沿)进行数据采样。

- 当CPHA=1时,在时钟的第二个跳变沿进行数据采样。

SPI硬件电路

主器件由一个移位寄存器、一个数据锁存器和一个时钟发生器组成。 从机由类似的硬件组成:移位寄存器和数据锁存器。 两个移位寄存器相连形成一个回路。

- 在时钟信号的上升沿期间,两个设备(主设备和从设备)都将输入位读入寄存器的

LSB。 - 在时钟信号的负周期期间,主机和从机都在移位寄存器的

MSB的相应输出上放置一个位。 - 对于每个时钟周期,在每个方向(即从主设备到从设备以及从设备到主设备)传输一个数据位。因此,从每个设备传输一个字节的数据需要 8 个时钟周期。

推挽输出

提供相对较好的信号完整性和高速。

菊花链配置

只有一条从属选择线连接到所有从属。主机的 MOSI 连接到从机 1 的 MOSI。从机 1 的 MISO 连接到从机 2 的 MOSI,依此类推。最后一个slave的MISO连接到master的MISO。

考虑主机将 3 个字节的数据传输到 SPI 总线。 首先,第一个字节的数据被转移到从站 1。当第二个字节的数据到达从站 1 时,第一个字节被推入从站 2。 最后,当第 3 个数据字节到达第一个从机时,第一个数据字节被移入从机 3,第二个数据字节被移入第二个从机。 如果 master 想要从 slave 获取信息,它必须发送 3 个字节的垃圾数据给slave,以便slave中的信息到达master。

- 参考:知乎 钟明国